# Design and Simulation of a Modified Single-Ended Primary-Inductor Converter for Use in Charging Low Voltage Battery Applications with the Approach of Increasing the Power Factor of the Converter

Puya Behnia

Shahrood university of technology

## ABSTRACT

In this paper, the goal is to achieve a high-reduced gain for low-voltage electric vehicle charger applications using a modified SEPIC without a diode converter. The non-bridge-free structure, as well as the simultaneous switching of switches, reduces control complexity. The extensive converter reductor is achieved through the switched inductor structures, which allows for the battery charge profile needed for low-voltage batteries. The function of the discontinuous current states not only facilitates the ability to correct the intrinsic power coefficient on the network side, but also reduces the size of the magnetic components. The DICM's operation also provides zero-current for switches and zero currents for high frequency diodes, thus minimizing losses associated with reverse diode recovery transfers.

**Keywords:** Single – Ended Primary – Inductor Converter, Total harmonic distortion, Power factor

## 1. INTRODUCTION

The SEPIC circuit is a DC-to-DC converter, with its name derived from the initials of the Single-Ended Primary-Inductor Converter. This converter can produce an output voltage that is lower, equal to, or higher than the input voltage. This is possible by regulating the duty cycle. The circuit consists of a boost converter followed by a buck converter, so it can be considered as a buck-boost, but with the advantage that the output voltage will also be the direction of the input voltage. Additionally, the voltage can be adjusted to maintain constant output voltage. For example, by using a feedback loop, input voltage fluctuations can be neutralized to ensure stable output voltage.

### 1.1 Background

In this study, the modified SEPIC converter is implemented to the grid-connected PV system simulation using PSIM software for 15 kW power rating. The modified SEPIC converter is developed by combining conventional SEPIC converter, Boost converter and diode-capacitor circuit. The conventional step-up converters are also implemented in these systems and compared to the performance of modified SEPIC converter which is tested under various conditions both irradiance and ambient temperature changes. For all tests, the modified SEPIC converter is more efficient and has high stability for maintaining static gain by rectifying the quality of output voltage.[1] This paper proposes a new high-gain dc-dc converter suitable for high voltage and renewable energy applications. The proposed converter employs a single power switch, simplifying the control process. It integrates a coupled inductor and a voltage boosting module to achieve high output voltage applicable for DC microgrid and EV charging systems. Because of the unique design of the coupled transformer, the proposed converter attains a high voltage gain for a low and easily controllable value of the duty cycle. Unlike the conventional impedance source topologies and most other high voltage gain DC-DC topologies, the proposed MCQ-MSC provides a wide control range of switching duty cycle instead of the narrow range. The presented converter not only inherits the advantages of the non-isolated

transformer types of quadratics and SEPIC converters but also offers a higher voltage transfer ratio with the low normalized voltage stress across its semiconductors. Besides, a clamping circuit provides a safe path for the leakage inductance energy and avoids generating voltage spikes across the power switch. Finally, experimental results have been presented to verify the proposed converter's operation.[2] A new structure of high gain modified SEPIC DC-DC converter has been introduced for renewable energy applications. High voltage gain and continuous input current are the advantages of MSC. The working principle of MSC in CCM and DCM mode has been presented. Additionally, the mathematical voltage gain derivation in CCM and DCM mode with non-idealities consideration and parameter design has been shown sequentially. Also, overall comparison between MSC and other non-isolated single switch converters has been addressed. The performance of the proposed converter is tested with numerical simulation and hardware implementation for 100 W prototype model. The results are shown for 172 V output from 24 V input supply with a gain of almost 8. According to the obtained results, it can be concluded that the proposed converter is well suited for high voltage renewable energy applications.[3] In a variety of applications, such as automotive electronics, portable devices, and renewable energy systems, SEPIC converters are utilized. These applications involve situations in which the input voltage can demonstrate significant variation. The modified SEPIC converter is a solution for high voltage renewable energy application. In order to avoid high current during starting, the regulated dc supply is used. The high frequency component is incorporated to reduce the size of the components and the ripples in output current and voltage waveform. The analysis on voltage gain has been done in this study by considering some factors like internal resistance of diode, controlled semiconductor and inductor. The ability of the SEPIC converter to handle a wide range of input voltages is the primary benefit of this device. It is still able to produce a regulated output voltage, regardless of whether the input voltage is higher or lower than the voltage that is intended to the output. The efficiency of a SEPIC converter is contingent upon a number of factors, such as the input voltage range, the load conditions, and the particular implementation. When it comes to maximizing efficiency, proper design and component selection are absolutely essential.[4] A new modified SEPIC dc-dc boost converter topology is proposed and discussed in this paper. The operation of the proposed converter is theoretically analyzed in both CCM and DCM modes. The proposed converter has advantages such as less voltage stress of the switch, and diodes, less output voltage ripple, and high conversion efficiency. The expressions for the static voltage gain, voltage and current stresses of various components are derived. In addition, the expression for the output voltage with non-idealities and design guidelines are given sequentially. The conventional RCD clamps circuit has been used to reduce the voltage stress of the switch, and it helps to select the MOSFET with low  $r_{ds-on}$ , which reduces the conduction losses. Also, the loss due to device switching is diminished by the zero-voltage-switching technique. Therefore, the power loss of the proposed converter is less and hence increasing the conversion efficiency. The proposed converter is compared with the similar converter topologies and concluded that the proposed converter has better voltage gain with a smaller number of components.[5]

### 2.1.1 Converter's topology

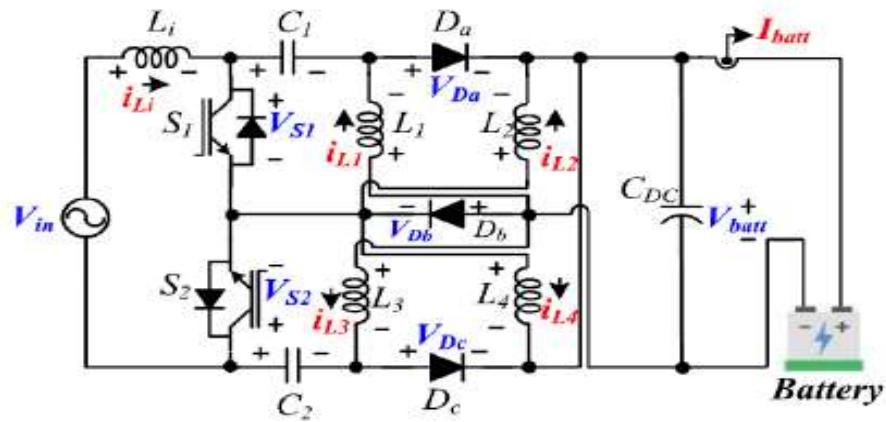

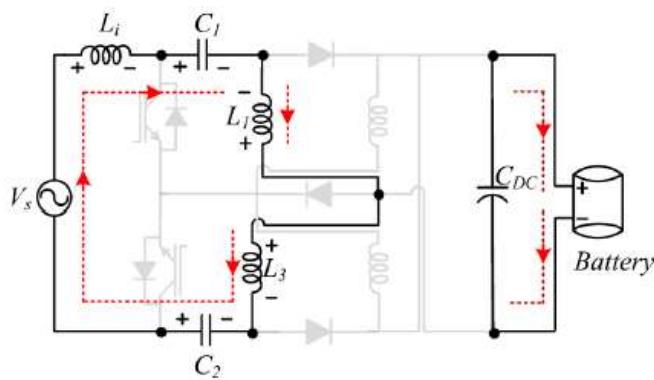

This converter is initially fed from a single -phase power supply at its input, which is subsequently followed by the LI input inductor and two-switches structure without S1 and S2, followed by the middle C1 and C2 capacitors. The L1-4 predecessors are switched in the structure and the  $D_{a-c}$  diodes are next step, then the DC link capacitor and the battery are connected to the output. The voltage reference orientations of each non-computed element in the converter are specified in the Figure 1.

Fig.1. The converter's topology

Performance analysis of the converter in the steady-state:

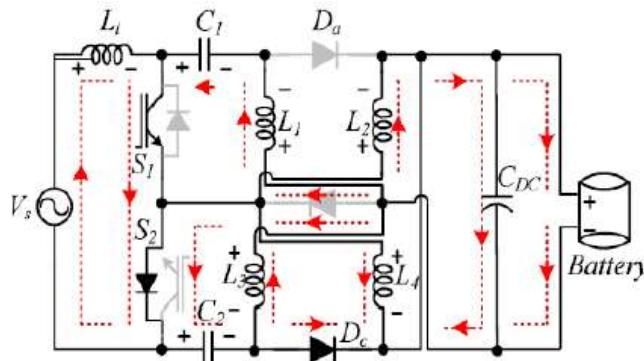

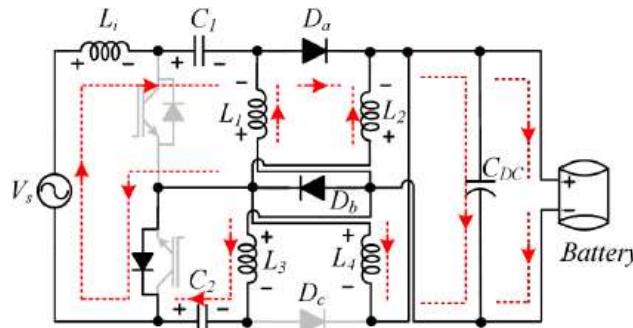

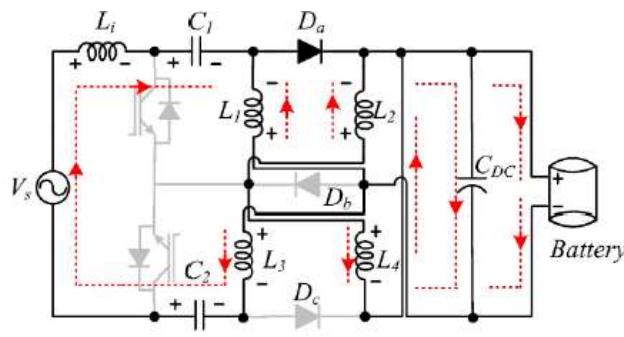

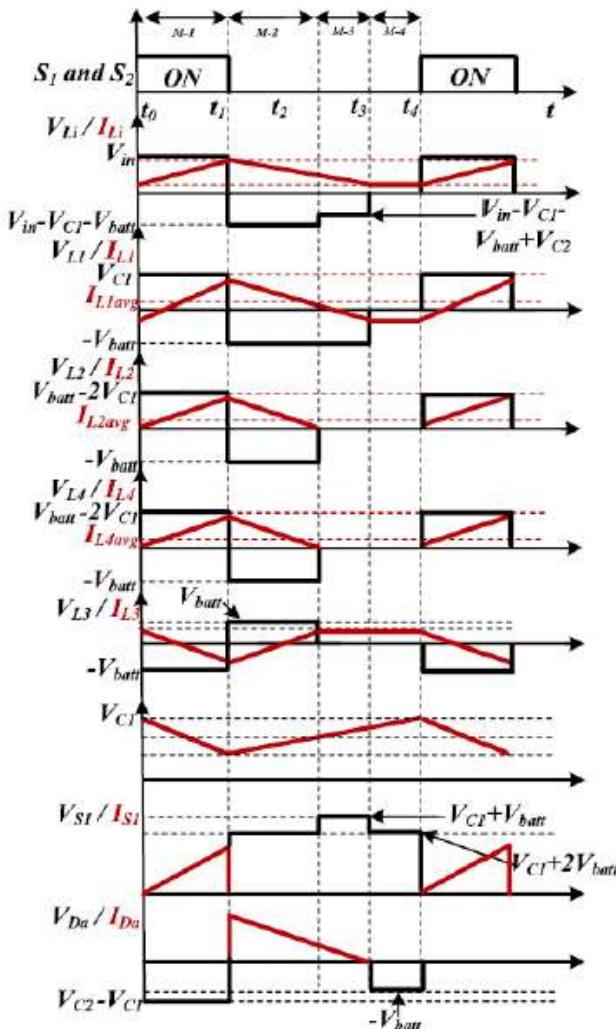

The suggested converter has four operational modes. Now different switches during all four modes in Figure 2 (A to D) is shown. Since the converter's performance is symmetrical in the negative half cycles. Only positive half-cycles are explained in this section. Rectified AC-to-DC currents and voltages waveforms are also shown in Figure 3 during each switching cycle.

(A)

(B)

(C)

(D)

Fig.2. The currents tracks and converter's operation modes in the time sequences of A) First time sequence B) Second time sequence C) Third time sequence D) Fourth time sequence

Fig.3. Currents and voltages waveforms in one complete cycle operation mode

Mode A (  $t_0$  to  $t_1$  ):

At the beginning of this mode, the S1 and the parallel diodes of the S2 are illuminated and the  $D_C$  also directs it during this mode. L1, L2 and L4 inductions are charged with positive current during this mode. However, L3 is discharged, meaning that the current through L3 is reduced by negative slope. The C1 is discharged and the C2 is charged during this mode, as shown in Figure 2.A. Voltages and currents are listed throughout the predecessors and capacitors during this mode in Figure 4.

Mode B (  $t_1$  to  $t_2$  ):

S1 turns off indicates the end of the first state as well as the start of the second state. During this mode, the S2 parallel diodes are directed along with diodes  $D_a$  and  $D_b$ , which causes negative voltage-drops across all predecessors, except L3, which is only under one positive voltage drop, as mentioned in Figure.4; This makes  $L_{in}$ , L1, L2 and L4 discharged, while the L3 is charged, and the  $I_{L3}$  has a positive slope. Capacitors C1 and C2 are charged during this mode. Current direction in this case in Figure 2.B is shown.

Mode C (  $t_2$  to  $t_3$  ):

The end of the second state is determined by stopping the  $I_{L2}$  and  $I_{L4}$  predecessors to zero and fixing the  $I_{L3}$  current at the end of the second state. During the third case, only the  $D_a$  directs, while other half-devices, including parallel diodes of the keys, remain on or in non-conductor. The equivalent circuit for this mode is in Figure 2.C.

Mode D (  $t_3$  to  $t_4$  ):

The turning off the all of the semi-conductor devices at the end of the third state shows the start of the fourth state. All switches turn off and zero voltage is available across the L1-4 inductions. During this operational state, the flow of the predecessors flows freely, as shown in Figure.2.

| Component | Mode-I                              | Mode-II                                            | Mode-III                               | Mode-IV                       |

|-----------|-------------------------------------|----------------------------------------------------|----------------------------------------|-------------------------------|

| $L_1$     | $V_a = V_s$                         | $V_a = V_s - V_{C1} - V_{sw}$                      | $V_a = V_s - V_{C1} - V_{sw} + V_{C2}$ | $V_a = V_s - V_{C1} + V_{C2}$ |

| $L_2$     | $V_{D1} = V_{C1} - V_{C2} - V_{sw}$ | $V_{D1} = -V_{sw}$                                 | $V_{D1} = V_{sw}$                      | $V_{D1} = 0$                  |

| $L_3$     | $V_{D2} = V_{C2}$                   | $V_{D2} = -V_{sw}$                                 | $V_{D2} = 0$                           | $V_{D2} = 0$                  |

| $L_4$     | $V_{D3} = -V_{sw}$                  | $V_{D3} = V_{C2}$                                  | $V_{D3} = 0$                           | $V_{D3} = 0$                  |

| $L_5$     | $V_{D4} = V_{C1}$                   | $V_{D4} = -V_{sw}$                                 | $V_{D4} = 0$                           | $V_{D4} = 0$                  |

| $C_1$     | $i_{D1} = -i_{D2}$                  | $i_{D1} = i_b$                                     | $i_{D1} = i_b$                         | $i_{D1} = i_b$                |

| $C_2$     | $i_{D2} = i_{D1} - i_{D4}$          | $i_{D2} = i_b$                                     | $i_{D2} = -i_b$                        | $i_{D2} = -i_b$               |

| $C_{DC}$  | $i_{DC} = i_b - i_{D1} - i_{D2}$    | $i_{DC} = i_b + i_{D1} + i_{D2} + i_{D3} - i_{sw}$ | $i_{DC} = i_b + i_{D1} - i_{sw}$       | $i_{DC} = -i_{sw}$            |

Fig.4. Capacitors currents and inductors voltages in each mode of the converter's operation

### 2.1.2 Converter's Design

The design of the components is based on the design criteria presented in Figure.5. The rated power is 450 watts and its feeding voltage is 220V (RMS), and is capable of operating in the 160-to-250-volt voltage range (RMS). The converter also has the ability to charge the battery with a voltage range of 36 to 72V. The further specifications required for the converter design are presented in Figure.5.

| S. No | Design Variables                                | Values    |

|-------|-------------------------------------------------|-----------|

| 1     | AC Input Voltage ( $V_{Smax} - V_{Smin}$ )(RMS) | 160-250 V |

| 2     | Supply voltage nominal value (RMS)              | 220 V     |

| 4     | Battery nominal Voltage ( $V_{batt}$ )          | 48 V      |

| 5     | Battery Voltage Range                           | 36-72 V   |

| 6     | $C_1 / C_2$ cut-off frequency                   | 1000 Hz   |

| 7     | Percentage Ripple in and $I_b$                  | 25%       |

| 8     | Switching Frequency ( $f_s$ )                   | 20 kHz    |

| 9     | Percentage Ripple in $V_{DC}$                   | 5%        |

Fig.5. The converter's characteristics

The elements passive values after calculating are:

|           |                   |

|-----------|-------------------|

| $L_1$     | $6 \text{ mH}$    |

| $C_1=C_2$ | $3 \mu\text{F}$   |

| $L_1=L_3$ | $45 \mu\text{H}$  |

| $L_2=L_4$ | $200 \mu\text{H}$ |

| $C_{DC}$  | $5 \text{ mF}$    |

Fig.6. The passive elements values of the converter

### 2.1.3 Design of the control circuit

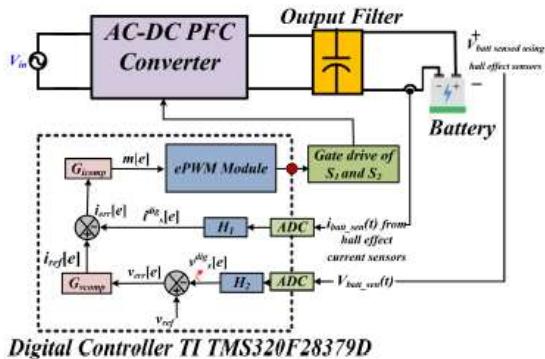

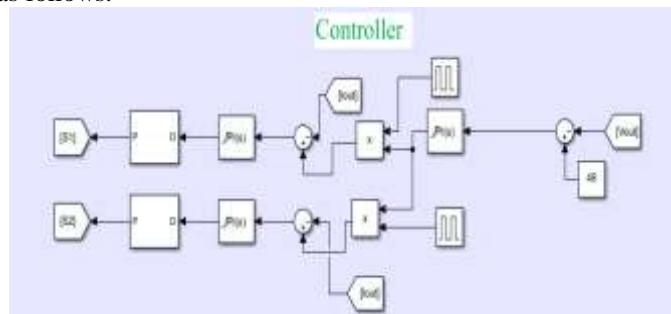

The digital converter control is implemented using the TMS320F28379D DSP processor. The control considers two modes: Constant current charging mode and Constant voltage charging mode. Therefore, a dual loop control is used in which the outer loop controls the  $V_{Batt}$  and the inner loop controls the  $I_{Batt}$  (Figure.7).

Fig.7. The complete block diagram of the converter

The battery voltage and current are sensed by  $V_{Batt}$  (SEN) and  $I_{Batt}$  (SEN), respectively, using an analog to digital DSP. For the outer loop,  $V_{Batt}$  (SEN) first passes from a low-pass filter and the output of the LPF is compared to the reference voltage of the battery. The error results are fed after comparison to a  $G_{V_{comp}}$  voltage PI compensator, which produces the reference current  $I_{ref}$  for the internal control loop. The reference stream of the  $I_{ref}$  is then used to compare with the filtered output of the  $I_{Batt}$  (SEN) via ADC. The resulting current error of the  $I_{err}$  is then fed to a PI compensator with integral coefficients and proportionate KI and KP. The output of the PI controller generates the  $M[e]$  signal accordance with the duty cycle of the converter. This process produces PWM pulses to control S1 and S2 switches.

### 3.1 Simulation results

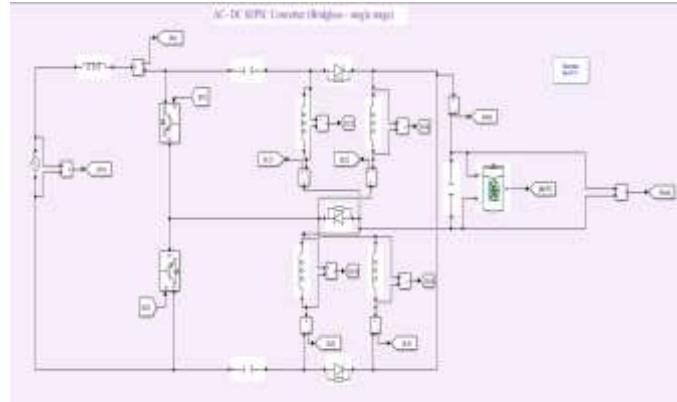

The topology of the converter in MATLAB software is as follows:

Fig.8. The topology of the converter in the MATLAB software

In this simulation to show the correct results and according to the duty cycle which is almost low, so the Sample Time must be at least 50  $\mu$ s. The input voltage is 260V. The battery voltage is 48V. The simulation of the controller part is as follows.

Fig.9. The block diagram of the converter's controller

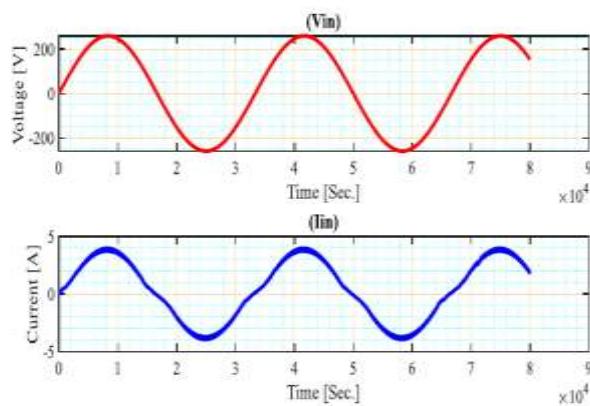

The input converter's current and voltage is as follows:

Fig.10. The input converter's current and voltage

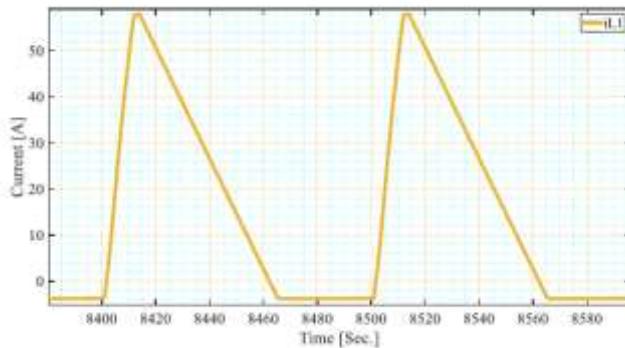

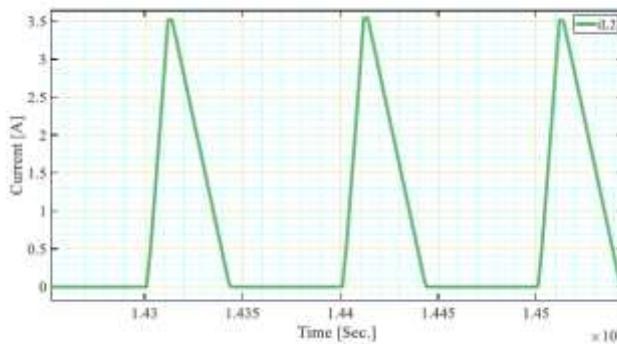

The inductors number 1 to 4 waveform are as follows:

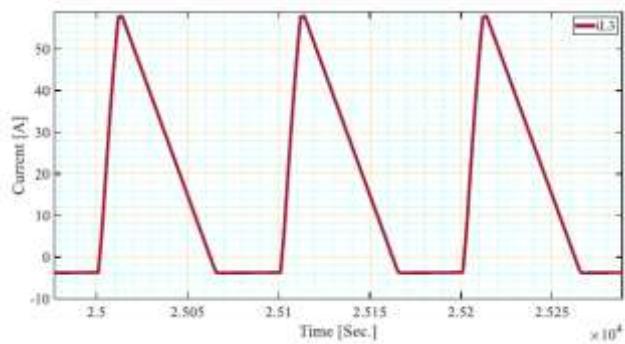

Fig.11. The inductor 1 current's waveform

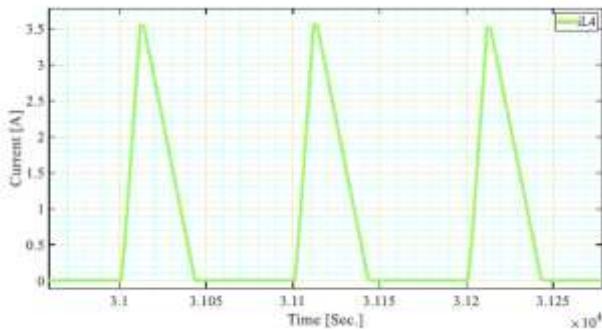

Fig.12. The inductor 2 current's waveform

Fig.13. The inductor 3 current's waveform

Fig.14. The inductor 4 current's waveform

As it can be seen in figure 10, the converter's simulated topology guarantees the 100% power factor with approximately the least distortion of  $I_{in}$ .

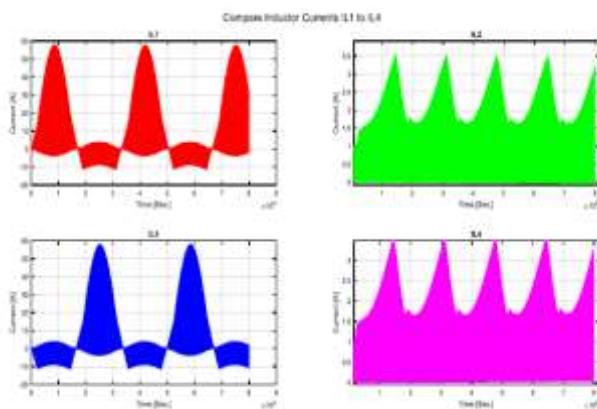

In the next figure the inductors DICM mode of operation is shown:

Fig.15. The inductors current

As it can be seen in figure 10 the converter's topology shows the potential power factor correction (PFC) features.

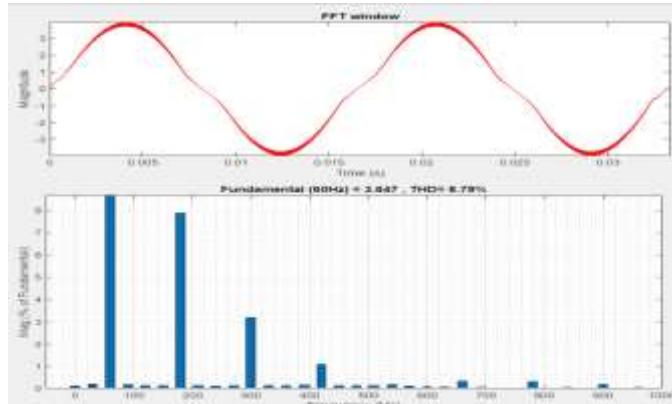

In the next figure the total harmonic distortion of the converter is shown which is 8.79% and is satisfactory:

Fig.16. The THD calculation by MATLAB software

#### 4.1 Conclusion

Power quality is one of the most important aspects of power electronics engineering. In this paper it is tried to design and simulate a modified SEPIC converter which shows potential features of a PFC itself which the

converter's THD is very low and is suitable for power electronics applications. In this converter the power losses during the power transmission process are achieved near to zero joules which is satisfactory. At last, a 48 DC Volts battery is charged by this converter as one of this converter's applications.

## REFERENCES

- [1] G. Eason, B. Noble, and I. N. Sneddon, "On certain integrals of Lipschitz-Hankel type involving products of Bessel functions," *Phil. Trans. Roy. Soc. London*, vol. A247, pp. 529–551, April 1955.

- [2] Esmaeili, S., Shekari, M., Rasouli, M., Hasanpour, S., Khan, A. A., & Hafezi, H. (2023). High gain magnetically coupled single switch quadratic modified SEPIC DC-DC converter. *IEEE Transactions on Industry Applications*, 59(3), 3593-3604.

- [3] Maroti, P. K., Padmanaban, S., Holm-Nielsen, J. B., Bhaskar, M. S., Meraj, M., & Iqbal, A. (2019). A new structure of high voltage gain SEPIC converter for renewable energy applications. *Ieee Access*, 7, 89857-89868.

- [4] Rao, D. S. N. M., Jasmin, M., Pandey, M., Almusawi, M., Ramadan, G. M., & Kumar, R. S. (2024). Efficiency Analysis Of Modified Sepic Converter For Renewable Energy Applications. In *E3S Web of Conferences* (Vol. 564, p. 01007). EDP Sciences.

- [5] Premkumar, M., Subramaniam, U., Haes Alhelou, H., & Siano, P. (2020). Design and development of non-isolated modified SEPIC DC-DC converter topology for high-step-up applications: investigation and hardware implementation. *Energies*, 13(15), 3960.